Genio Evo

A cross-fabric

platform

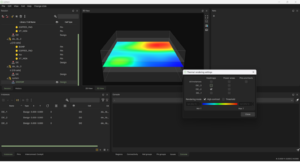

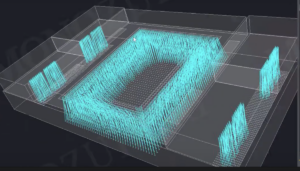

GENIO EVO is a cross-fabric platform for system design providing chiplets/die, silicon interposer, package, and surrounding PCB co-design features that achieve area, power, and performance targets.

It is technology agnostic and seamlessly integrates through standard formats with all existing commercial implementation platforms or to custom EDA flows through dedicated plug-ins.

HETEROGENEOUS

3D-INTEGRATION

Multi-physics

Design Cockpit

Advanced modeling

Mechanical Stress, Thermal, TSV

Architectural Exploration

and Connectivity Management

Streamlines a multitude

of packaging solutions

(CoWoS, InFO, SoIC, Foveros, EMIB, FoCoS, Swift, EFB…)

MZ

Technologies

Global Technology. European Culture.

Italian Workmanship.

MZ Technology

MZ technologies is the marketing function of Monozukuri S.p.A., a privately held EDA company based in Rome, Italy, directed by a team of EDA and Silicon veterans.

Exponential Innovation

We believe the future will be shaped by exponential innovation, and we’re committed to creating a technology design nexus that transforms visionary ideas into tomorrow’s reality.

Constant Development

MZ Technologies is visionary, innovative, and committed. Since 2015, we’ve developed EDA solutions for advanced packaging, enabling next-gen, vertically stacked ICs with superior time-to-market and yield-to-volume.

Timeline

What’s New

MZ Technologies To Exhibit at Chiplet Summit Unveils Next Generation Chiplet/Package Design Tool

Will highlight GENIO EVO next generation chiplet/package design tool MZ Technologies, a leading supplier of innovative solutions and methodologies for 2.5 and 3D design, will be exhibiting at Chiplet Summit,

MZ Technologies Updates Technology Roadmap

Tackling the barriers to 3D-IC design architecture MZ Technologies has unveiled an updated technology roadmap for its GENIOTM branded integrated chiplet/packaging Co-Design EDA tool. The roadmap calls for major improvements throughout

How GENIO Enables Multi-Die Design

MZ Technologies is a unique company that enables multi-die design by providing critical planning and analysis tools that sit above the traditional EDA design flow. Chip and package design tools